ARM Architecture

* Update history

- 2012.8.14 : �ʱ� Release

5. ARM Processor

5.1 ARM ������� ����

5.2 ARM Processor ����

6. ARM Architecture

6.1 ARM based system

6.2 ARM Operating Modes

6.3 ARM Registers

6.4 ARM Exceptions

6.5 Exception �� Interrupt�� ����

6.6 ARM������ Interrupt system

5. ARM Processor

4������� �б��ٴҶ� �ѹ����� ��� �R������ �������� �ټ� ������ �����̾��� �����ϴ�. ���� 5����� ���������� ARM �� ���ؼ� ������ ������ �ϰڽ��ϴ�.

ARM(����ȸ��) ��� architecture core �� system core �� License ���ִ� IP ȸ�� �Դϴ�.

���� �ݵ�ü�� �����Ͽ� �Ǹ��ϴ� ���� �ƴ϶� ������ ���μ����� �ݵ�ü ȸ�翡 Hard Macrocell(�����Ұ�) �Ǵ� Synthesizable core(�Ϻ� ���� ����) �� ���� �մϴ�.

�ݵ�ü ����ȸ�翡���� ARM��� ���� �������� ARM core�� �ֺ� ��ġ�� �߰��Ͽ� SOC�� ����� ����ڿ��� �Ǹ��ϰų� ��ü ��ǰ�� ��� �մϴ�.

������ �Ʒ� ������� �ֱ� ARM���� ���� �Դϴ�. Cortex-M3(2004��), M0(2009��), M4(2010��), ���� ��ǥ�� � ���� �˼��� �ֳ�.

2012

- ARM, Gemalto and G&D form joint venture to deliver next-generation mobile security

- First Windows RT (Windows on ARM) devices revealed

- ARM, AMD, Imagination, MediaTek and Texas Instruments founding members of Heterogeneous System Architecture (HSA) Foundation

- ARM and TSMC work together on FinFET process technology for next-generation 64-bit ARM processors

- ARM forms first UK forum to create technology blueprint “Internet of Things” devices

- ARM named one of Britain’s Top Employers

- MIT Technology Review named ARM in its list of 50 Most Innovative Companies

2011

- ARM ranked #12 in FastCompany’s 50 Most Innovative Companies

- WIRED magazine named Warren East in the UK’s Most Influential Leaders

- ARM CEO Warren East makes Barron’s list of the World’s Top 30 CEOs

- ARM was again included in the FTSE4Good Index, designed to measure the performance of companies that meet globally-recognized corporate responsibility standards

- ARM granted Queen’s Award for Enterprise (Innovation Category)

- Microsoft unveils Windows on ARM at CES 2011

- IBM and ARM collaborate to provide comprehensive design platforms down to 14nm

- ARM and UMC extend partnership into 28nm

- Cortex-A7 processor launched

- Big.LITTLE processing announced, linking Cortex-A15 and Cortex-A7 processors

- ARMv8 architecture unveiled at TechCon

- AMP announce license and plans for first ARMv8-based processor

- ARM Mali-T658 GPU launched

- ARM expands R&D presence in Taiwan with Hsinchu Design Center

- ARM and Avnet launch Embedded Software Store (ESS)

- ARM, Cadence and TSMC tape out first 20nm Cortex-A15 multicore processor

2010

- Giesecke & Devrient secure mobile payments announcement via ARM TrustZone and G&D's Mobicore technologies

- ARM launches Cortex-M4 processor for high performance digital signal control

- ARM together with key Partners form Linaro to speed rollout of Linux based devices

- Microsoft becomes ARM Architecture Licensee

- ARM & TSMC sign long-term agreement to achieve optimized Systems-on-Chip based on ARM processors, extending down to 20nm

- ARM extends performance range of processor offering with the Cortex-A15 MPCore processor

- ARM Mali becomes the most widely licensed embedded GPU architecture

- ARM Mali-T604 Graphics Processing Unit introduced providing industry-leading graphics performance with an energy-efficient profile

- ARM announces Corelink 400 series of AMBA 4 protocol-compliant system IP

2009

- ARM announces 2GHz capable Cortex-A9 dual core processor implementation

- ARM invests in Japanese software vendor eSOL to develop enhanced platforms for next-generation automotive electronics

- ARM launches its smallest, lowest power, most energy efficient processor, Cortex-M0

- ARM Ltd. receives Best Companies accreditation

- ARM extends its leadership in media processing by acquiring Logipard AB

2008

- ARM announces 10 billionth processor shipment

- ARM wins Britain's Top Employer Award 2008 from crf.com

- ARM announces Industry First silicon-on-Insulator Physical IP for IBM's 45nm SOI Foundry

- ARM Mali-200 GPU Worlds First to achieve Khronos Open GL ES 2.0 conformance at 1080p HDTV resolution

2007

- Five billionth ARM Powered processor shipped to the mobile device market

- ARM Cortex-M1 processor launched – the first ARM processor designed specifically for implementation on FPGAs

- AMBA Adaptive Verification IP launched

- RealView Profiler for Embedded Software Analysis introduced

- ARM unveils Cortex-A9 processors for scalable performance and low-power designs

- ARM Introduces SecurCore SC300 Processor For Smart Card Applications

- Warren East, CEO, wins Orange Business Leader of the Year Award

2006

- IEEE honors ARM with its 2006 Corporate Innovation Recognition award.

- ARM Cortex-A8 processor recognized as "Best In 2005" by four leading electronics industry publications

2005

- ARM listed by Electronic Business as one of the ten most significant companies in electronics over the past 30 years

- ARM acquired Keil Software

- ARM Cortex-A8 processor announced

- ARM launched DesignStart Program

2004

- ARM acquired Artisan Components Inc.

- The ARM Cortex family of processors, based on the ARMv7 architecture, is announced. The ARM Cortex-M3 is announced in conjunction, as the first of the new family of processors

- ARM Cortex-M3 processor announced, the first of a new Cortex family of processor cores

- NEON media acceleration technology announced

- ARM technology licensed to Aplix, Atheros, Broadcom, CSR, Kawasaki, NEC, Socle, Sony Ericsson, Thomson, Toshiba, Samsung and ZRRT

- ARM acquired Axys Design Automation

- MPCore multiprocessor launched, the first integrated multiprocessor

- OptimoDE technology launched, the groundbreaking embedded signal processing core

5.1 ARM ������� ����

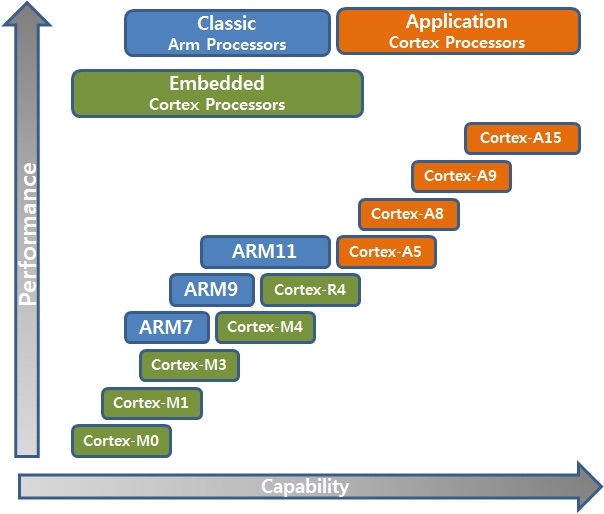

ARM Processor�� ���ؼ� ������� ������ �غ� ���Դϴ�. �� ǥ�� �ٸ��� �з��� �ϴ� ����鵵 �ֽ��ϴ�. �̰��� �� �������� �Ǵܿ� ���� �з� �Դϴ�.

Cortex ���μ��� ������ ARM Processors���� �������� ARM���� �з� �Ͽ��� Cortex-M, R �ø��� ������ ������ uCOM������ ���μ������� �ܳ��� �����̸鼭 Realtime ���μ��� ������ �ܳ��� ���μ��� �̰�, A �������� ���ʹ� �������� Application�� �����ϴ� ���μ����� �з� �Ͽ����ϴ�.

5.1.1 ARM7 Processor

(1) ARM7TDMI Core

- RISC Architecture (ARM v4T)

- 3 stage pipelining

- Hard macrocell

- 32-bit ARM/16-bit Thumb Instructions

- Unified bus architecture( �����̸� ���� ����)

- ARM720T = ARM7TDMI + MMU + Cache(8KB Unified) + WB + AMBA

- S3C44B0 ��

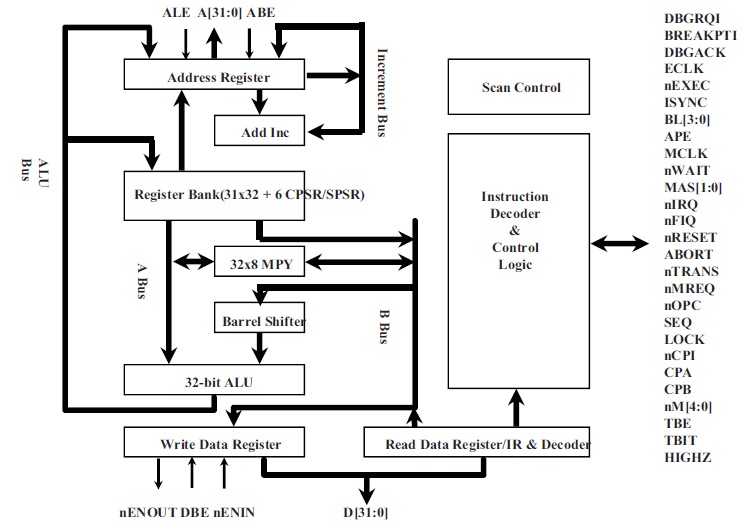

(2) ARM7TDMI Block Diagram

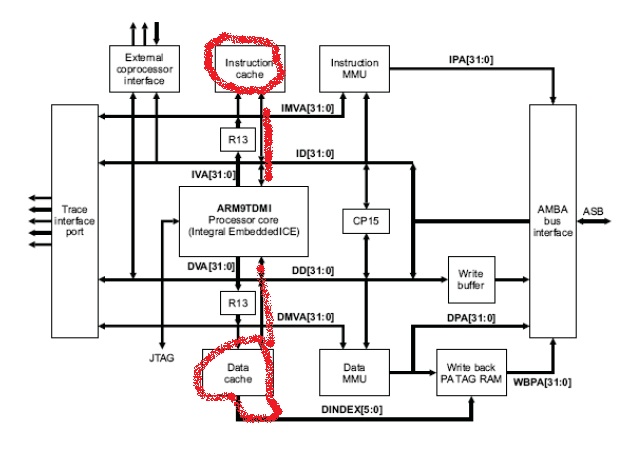

5.1.2 ARM9 Processor

(1) ARM9TDMI Core

- RISC Architecture (ARM v4T)

- 5 stage pipelining ->

Improved clock frequency

- Harvard Bus Architecture

- Simultaneous access to instruction and data memory

- Hard macrocell

- 32-bit ARM/16-bit Thumb Instructions

- ARM920T = ARM9TDMI + Dual Caches + MMUs + WB + AMBA + PA TAG RAM

- S3C2440, S3C2443 ��

���� ARM7�� �� ���ɾ� ������ ������ ������ ������ �Ǿ� �ִ°��� �˼� �ֽ��ϴ�. ���⼭ �ణ ������ �� ���̴µ���, Write back PA TAG RAM �� ����� ?

�� �� �����ϱ� ���ؼ��� ���� ij�� ���� 2���� ���� ����� �˾ƾ� �մϴ�. Cache���� ������ �ָ� Write�Ҷ�, Write-through ��İ� Write-back ����� �ֽ��ϴ�. Write-through����� ij�� ���� ������ ������Ʈ �ɶ� �� ���� ���ÿ� ������Ʈ�� �Ǵ� ����̰� Write-back ����� ij�ø��� ������ ������Ʈ �Ǿ �ٷ� �� �� �ݿ��� �Ǵ� ���� �ƴ϶� Write back PA TAG RAM ���� ��� ������ �ξ��ٰ� ���� ������ CPU�� ���� �ִ� ���ȿ� �� �� ������Ʈ �ϴ� ��� �Դϴ�. Write Buffer�� Write-throuh ����� ��쿡 Data Cache�� ������ �� �� Write �ϱ� ���� Buffer ������ ���ְ�, Write back PA TAG RAM�� Write-back ����� ��쿡 Data Cache�� ������ ��� �����ϰ� �ִٰ� �� �� Write�� ���ִ� ������ �մϴ�.

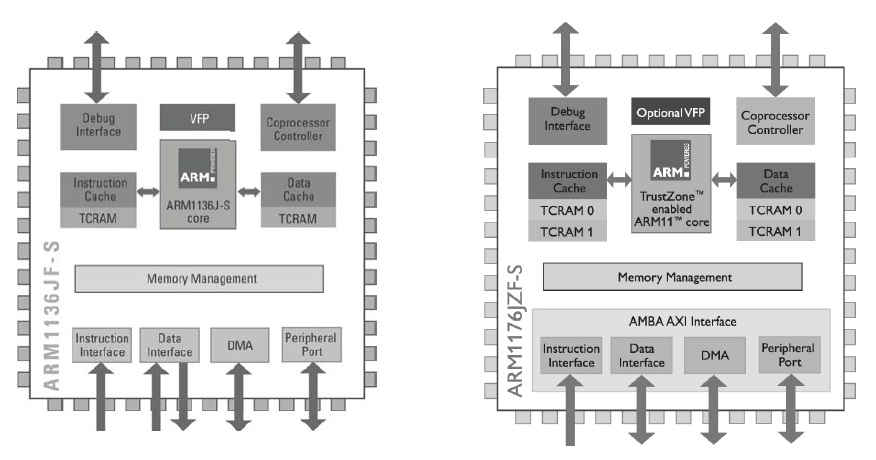

5.1.3 ARM11 Processor

(1) ARM1176JZ(F)-S Core

- ARM v6 Architecture

- Improved Multimedia Performance

2x faster MPEG4 encode/decode

SIMD(Single Instruction, Multiple Data) Instructions : ���� �������� ���� ������ ó���ϴ� ���� ���մϴ�.

- Improved Real-Time Performance

Fast Exception/Interrupt Handling

Vector Interrupt Controller -> Reduced Interrupt Latency

New Stack and Processor Mode Change Instructions

- Improved Memory Interface

Un-aligned Data Access

Mixed-Endian

8 stages pipeline

Higher clock frequency

9 stages pipeline for ARM1152T2(F)-S

Separate load-store and arithmetic pipelines

Branch prediction (static & dynamic)

Return Stack

- Other features

High Performance Integer Processor

Physically-tagged caches

Jazelle technology

VFP (Vector Floating Point)

Non Blocking

HUM (Hit Under Miss)

ARM TrustZone Technology

Thumb-2 Instruction

Intelligent Energy Manger (IEM) Technology

- S3C6400, S3C6410 ..

5.1.4 ARM Cortex Families

(1) A profile (ARMv7-A) : Application Profile

- For sophisticated, high-end applications running open and complex operating systems

- ARM, Thumb, Thumb-2 instruction sets

- S5PC100, S5PV210, OMAP3530 ..

(2)

R profile (ARMv7-R) :

Real-time Profile

- For real-time system

- ARM, Thumb, Thumb-2 instruction sets

(3) M profile (ARMv7-M) :

Microcontroller Profile

- For cost-sensitive and microcontroller applications

- Thumb-2 instruction set only

- STM32F �ø���

�����ӰԵ� ���� ��ǥ�� Cortex �йи��� Profile�� ù��° �̸��� A.R.M ���� ȸ�� �̸��� ���� �ϳ�. �쿬�� ��ġ �ΰ���? ^^

5.2 ARM Processor ����

- Embedded real-time Processor

Embedded real-time systems for storage, automotive body and powertrain,

industrial and networking applications

- Application Processor

Devices running open operating systems including Linux, Palm OS,

Symbian OS and Windows CE in wireless, consumer entertainment and

digital imaging applications

- Secure Processor

Smart cards, SIM cards and payment terminals

���� ���� ���������� �з� �� ���� �ְ����� �ᱹ ���������� ���μ��� ������ ���� ū ������ ���ݴ�� ������ ���Դϴ�. ���� �����Ϸ��� �ϴ� ������Ʈ�� ���� �� �� �ִ� ���� ���� Cost�� ���μ����� ���� �� ���̱� ���� �Դϴ�. ���� ������ Money, Money �ص� �Ѱ� �ְ���. ���⼭ �� �Ѱ��� S/W �������� ���忡�� ������ ���� ������ ���̵��� ���Դϴ�. �������� ARM�� �ش��ϴ� ARM7, ARM9, ARM11 ���μ������� RAM, ROM�� CPU�ܺο� ��ġ ��ŵ�ϴ�. �̷��� ����(CPU, ��ǰ���� �ּҿ� �ʱ�ȭ �ڵ���� Ʋ����)������ �ڵ��� ȣȯ��( ����ϴ� �� ��ũ�� ���� �뷮, ������ ���� �ҽ� ������ �ڵ尡 ����)�� �ſ� �������� ��Ʈ�δ� ���� ���� �ۼ� �ؾ� �մϴ�. �̿� ���ؼ� Cortex-M, R ���������� �ھ���� CPU���ο� RAM, ROM�� ������ �ְ� Address ���� ���� �ھ ����ϴ� CPU���� ��� ���� �ϰ� ���˴ϴ�. ���� �����Ϸ�(���� IDE) ���ؿ��� ��Ʈ�δ��� ���� �� ���� �ֽ��ϴ�. ������ ��κ��� ��� �����Ϸ� ���� �����ڰ� ��Ʈ�δ� �ڵ带 �ۼ����� �ʾƵ� �⺻���� �����ϰ� �ֽ��ϴ�.

6. ARM Architecture

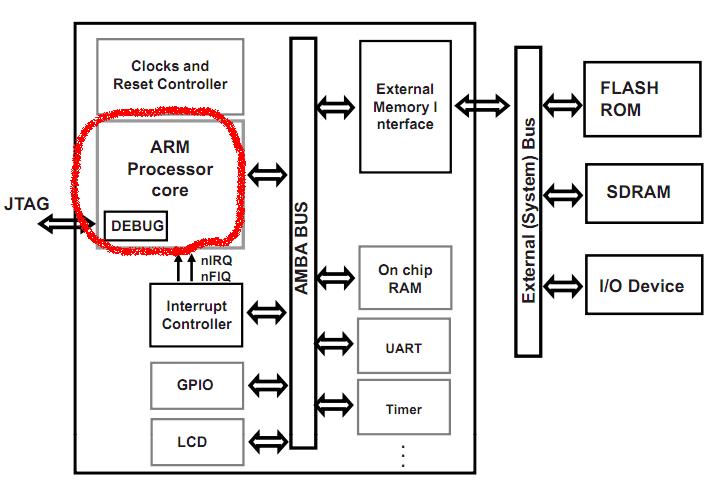

6.1 ARM based system

���� �������� ARM Core�� ���� �������� �ƴϰ� ������ �κ��� ARM Core�� �̿��ؼ� ������ CPU�� �� �� �Դϴ�.

6.2 ARM Operating Modes

(1) 7���� Processor Mode�� ����

User, FIQ, IRQ, Supervisor, Abort Mode, Undefined, System Mode

(2) Operating Mode ������ Hardware �� Software�� ���� �մϴ�.

ARM ���μ����� ������ �ΰ� �Ǹ� SVC ��忡�� ������ �ǰ� ���ͷ�Ʈ, �ͼ��� ���� ���ϸ� ��Ȳ�� ���߾ H/W ������ Operating Mode �� ������ �ǰų� S/W �����δ� SWI ���ɾ ���ؼ� SVC ���� ���� �� ���� �ֽ��ϴ�.

ARM Core���� �� �̷��� �������� ���� ��尡 �����ϴ� ���ϱ��? �Ƹ��� ��Ű���� �������� ����Ʈ������ ���ȹ� ������ ���� �ϱ� ���ؼ��� ���Դϴ�. ���� OS ����� Ŀ�� S/W �� ��� ������ ������ ���� �ϵ��� �ϰ�, User ���ø����̼��� ���ѵ� ������ ������ ������ �ϵ��� ���� �Ѵٸ� ���ø����̼� ���μ����� ��� ������ ���� User Mode ���� ���� ��Ű�� ������ Ŀ�ι� ����̽� ����̹����� ������ �ִ� ������ ���(Supervisor, System Mode)���� ���� ��Ű���� �� �� �ֽ��ϴ�. ���� �̷��� ����� S/W �����ε� ������ �Ұ����� ���� �ƴ����� ������ ���ؼ��� �� ���� ����� �ʿ��� ���Դϴ�.

| Mode | Description | |

| Supervisor(SVC) | Entered on reset and when a Software Interrupt instruction (SWI) is executed | Privileged modes |

| FIQ | when a fast(urgent) interrupt occurred | |

| IRQ | when a normal interrupt occurred | |

| Abort(ABT) | when a data fetch or instruction prefetch aborts | |

| Undef(UND) | when an undefined instructions is executed | |

| System(SYS) | Privileged mode using the same registers as User mode | |

| User(USER) | Mode under which most Applications / OS tasks run | Unprivileged mode |

- CPSR Register�� Privilege Mode ���� S/W �� ���� ����, User Mode���� �����ϸ� Undefined Instruction Exception �� �� �մϴ�.

- ARM Core�� ������ �ΰ��Ǹ� ���ʿ��� Supervisor ���� ������ �մϴ�. ó���� ������ ���� ���� ������ �ϸ� Privilege Mode�� ��ȯ �� ����� ������.

- �� ���� ������ Stack������ Banked Register ������ ������ �ֽ��ϴ�.

������ �������� ��尡 ���� ������ ���� � ��带 �ݵ�� ��߸� �ϴ� ��Ģ�� �ִ� ���� �ƴϰ�, �Ϲ� ���� �ǰ� ������ ���Դϴ�. ��κ� OS�� ����� �ʴ� �ܼ��� �߿��� ������ �ڵ���� �ʱ� ���ý� ������ Supervisor �� ����ϴ� ��쵵 ���� �ֽ��ϴ�. ���� ǥ�� ���� mode�� ũ�� Privileged modes�� Unprivileged mode �� ���� �� �ֽ��ϴ�. 2���� mode ������ ���̴�

(1) Privileged Mode (Ư�� ���)�� IRQ�� FIQ���� Interrupt�� ��� ���� ������ ���� ���� �� �� �ֽ��ϴ�.

(2) Privileged Mode�� �ڱ�鳢�� ���� Mode ������ ��������� ���� �մϴٸ�, Normal Mode�� �ڱ� ������ Privileged Mode�� Mode�� ������ �Ұ��� �մϴ�.

�װ��� ���� ���, SYS ↔ FIQ, IRQ ↔ SVC�� ���� Privileged Mode → Normal Mode (USR)�� ����������, USR → Privileged Mode���� ������ �Ұ��� �մϴ�. ���� �߿��� ����Դϴ�. ����� �ּ���. �ᱹ Privileged Mode�� �ڱ�� �ڴ�� Mode�� ���� �� �����Ӱ� �Դ� ���� �� �� ������, USER Mode�� �������� �ʽ��ϴ�.

FIQ, IRQ, Abort, Undef ���� ������ �忡�� ���� �ڼ��� ���� �ϵ��� �ϰ� System mode, User mode, Supervisor (SVC) mode �� ���ؼ� ���� ���� �ϵ��� �ϰڽ��ϴ�. User Mode�� Application Program�� Execution �ϴ� Mode�̰�, System Mode�� Privileged Operating system task�� ����Ǵ� mode�̰�, Supervisor mode�� ��ȣ�� Operating system(Ŀ�ε�) ���� �ַ� ���Ǵ� mode �Դϴ�.

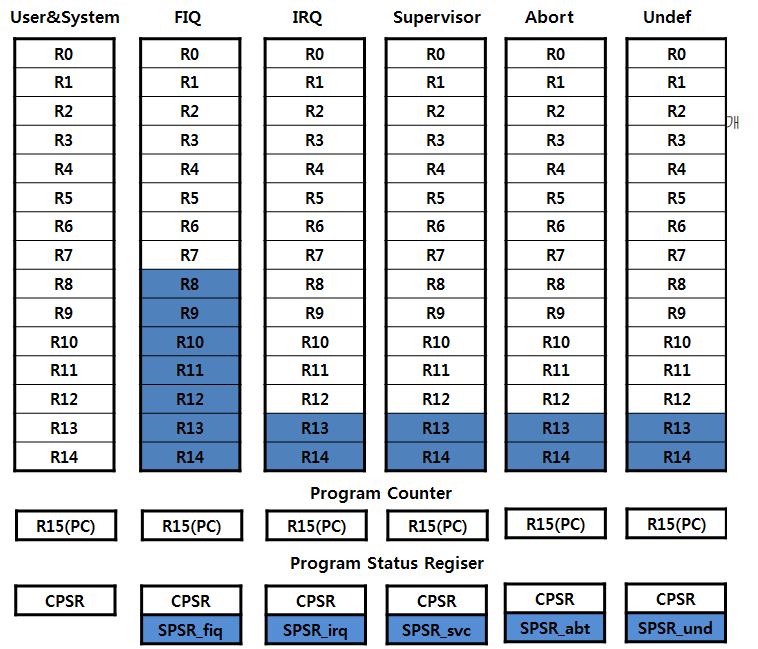

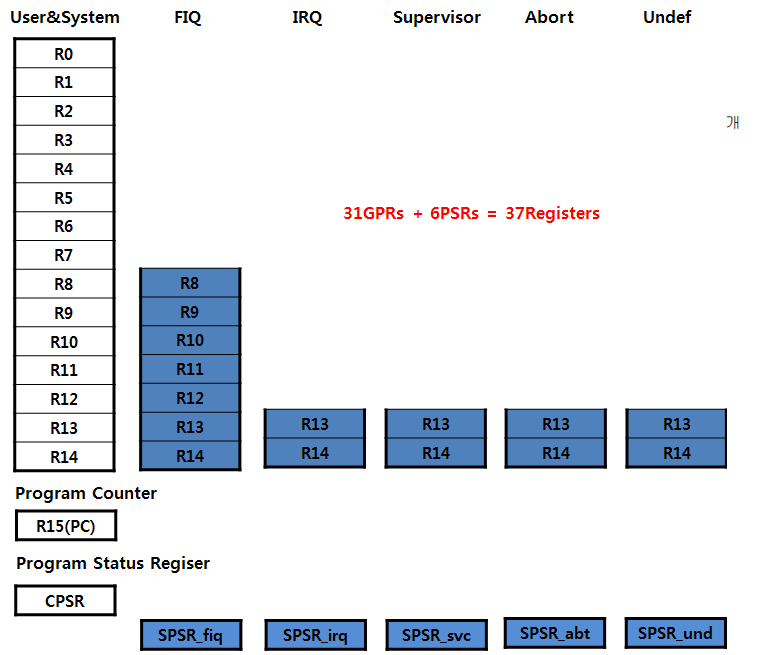

6.3 ARM Registers

6.3.1 Normal Registers

�� �ð��� �������ʹ� �ӽ÷� ������ �����ϰ�, ���꿡 ���ǰ�, ���α� ��� ���Ǵ� ���ټӵ��� ������� �ӽ� �����ġ ��� ������ �Ͽ����ϴ�.

ARM Core�� �� �����ϱ� ���ؼ��� ARM Core�� ����Ǿ� �ִ� �⺻ Register���� ��� �����Ǿ� �ְ�, ���Ǵ����� �� �˾ƾ� �մϴ�. Register���� Core�� ����� �� �ִ� ���� ��ü �߿��� ���� ���� �ӵ��� �ڶ��ϸ�, ARM�� ������ ��� Register���� ��� ����ϴ³Ŀ� ���� ������ ���� �� �� �ֽ��ϴ�. �ᱹ ARM ���μ����� ��� �Ѵٴ� ���� �Ʒ� Register���� ������ ������ �ϸ� �� �� �� ���ε� �ֺ� ��ġ���� �����ϱ� ���ؼ� Load, Store �ϴ� ���Դϴ�.

���� �������� ���� ���� ARM ���۸�庰�� ������ �Ǿ� �ְ�, ���� ��忡 ���� �Ķ��� �ڽ��� �ѹ� �� ������ �Ǿ� �ִ°��� �� �� �ֽ��ϴ�. �Ķ��� �ڽ��� �Ǿ� �ִ� �������͵��� ��ũ�� �������Ͷ�� �մϴ�. ���ϱ� �����ڽ��� �������ʹ� ���� ��忡 ��� ���� �������� ���Ǿ����� �Ķ��� �ڽ��� ��ũ��� �������ʹ� ���� ��庰�� ���������� ��� �����ϴٴ� ���Դϴ�. ���θ� �ؼ��� �� ���ذ� ���� ������.

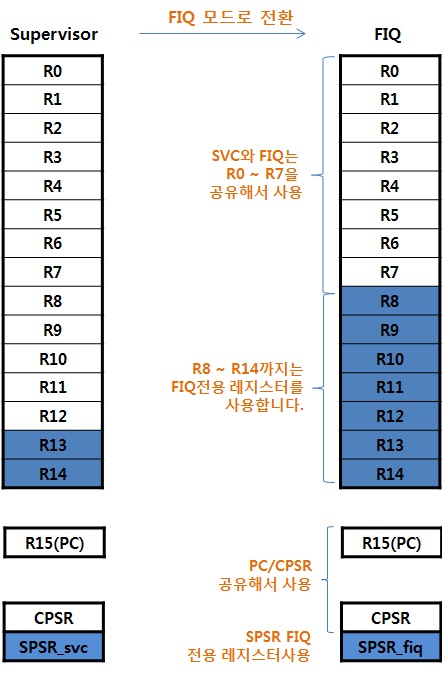

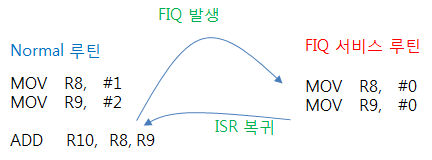

�Ѱ��� ���� �� ������ �ϵ��� �ϰڽ��ϴ�. CPU�� ���� ������ �ΰ��Ǿ� SVC ���� ������ �ϴٰ� FIQ���ͷ�Ʈ�� �� �Ͽ��� ��� �������� ���´� �Ʒ��� �����ϴ�. FIQ�� ��ȯ�� �Ǹ� R8 ~ R14������ FIQ���� �������Ͱ� ����� �˴ϴ�. �̸��� FIQ��忡�� R8 ~ R14�� SVC��忡���� R8 ~ R14�ʹ� �ٸ� �������� �Դϴ�. �� SVC��忡�� FIQ�� ���� �Ǿ����� ����(Context) ������ ���ؼ� R8 ~ R14�� ������ ���� �ʾƵ� FIQ��忡�� R8 ~ R14�� ������� ����ص� �˴ϴ�. CPSR�������͵� FIQ, SVC ��忡�� ���� ���� �մϴ�.

���⼭ ����(Context)�̶�� �� �����µ�, �����̶�� �ǹ̰� �����ϱ��?

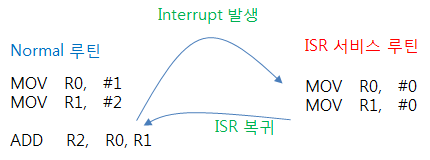

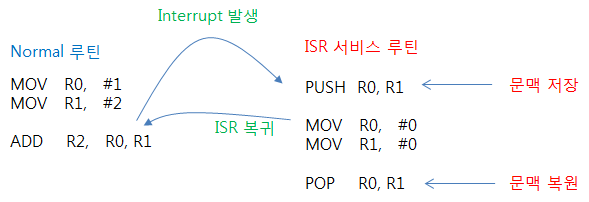

S/W ���忡�� ������ ���� ���α��� ������� ������ �Ǵٰ� � ������ ISR�� ���� �ϸ� ������ ���α� ������ ��� �ߴ��ϰ� ISR ���� ��ƾ���� �̵��ϰ� �˴ϴ�. �̶� ISR���� ��ƾ���� �̵��� �ϴ°��� ������ ��ȯ�̶�� �ϴµ��� ISR ���� ��ƾ���� �̵��ϰ� ���� ISR���� ��ġ�� ������ ���α��� ����ؼ� ������ �Ǿ�� �ϴµ� ���� ISR���� ��ƾ���� Ư�� �������͵�(R0 ~ R12)�� ����Ͽ��ٸ� �� ������ ������ �Ȼ��¿��� ������ ���α��� ����Ǵ� ��ġ�� ���ƿͼ� ��� ������ �ϰ� �Ǹ� ������ �ʴ� ����� ���� �� �ֽ��ϴ�. �̷��� ���� ������ ������ ������ ���ؼ� ISR ���� ��ƾ���� �̵��� �ϱ� ���� ISR���� ���� �������͵��� ���ÿ� �ӽ÷� ������ �ϰ� ISR��ƾ�� ���������� ���� ���ÿ� ����Ǿ� �ִ� �������͵��� �ٽ� �������� �ݴϴ�.

ISR ���� ��ƾ���� �̵��ϴ� ���� ������ ��ȯ�̶� �ϰ�

ISR ��ƾ���� ��� �� �������͵��� �ӽ÷� ���ÿ� �����Ͽ��ٰ� ISR��ƾ�� ������ ��ġ�� �����ϱ����� ������ �ξ��� �������͵��� ������ ������ �����ϴ� ���� ���� ���� �̶�� �մϴ�.

�� ~~ ������ ��� ������ ���ҳ�. �̰͵� �����ϰ� ���� �� �ٽ� ������ �ϵ��� ������.

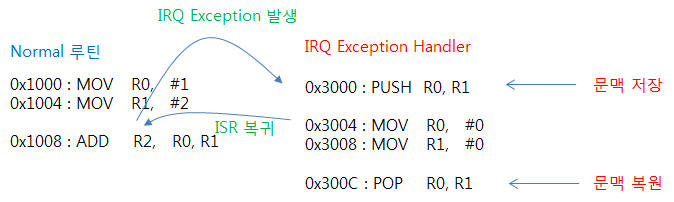

���� ������ "MOV R1, #2" ���� ���Ŀ� Interrupt�� ������ �ʾҴٸ� R2���� #3�� �� �־�� �ϳ� ISR ���� ��ƾ���� R0, R1�� #0���� �����Ͽ� ISR ��ƾ ���� �� R2���� #0�� �� �ֽ��ϴ�. �̰��� ������ ���ϴ� ���μ��� �帧�� �ƴմϴ�.

���� �������� ������ �̿��ؼ� ISR ���� ��ƾ���� ���� ����(PUSH)�� ����(POP)�� �ϰ� �־�

Interrupt�� ���Ͽ� ������ȯ(Context Switch - ISR ���� ��ƾ���� �̵�)�� �Ͼ �Ŀ���

���� �Ͽ����� R2���� ���������� #3�� �� �ֽ��ϴ�.

���� ������ FIQ ���ͷ�Ʈ�� �� ���� ����� ���� �Դϴ�. R10�� ����Ǵ� ���� ���ϱ�� ?

������ #3�� �� �ְ���. �ֳ��ϸ� FIQ ��忡�� ���Ǵ� F8 ~ R14�� ��ũ�� �Ǿ� �־ Normal��ƾ���� ���Ǵ� R8 ~ R12�ʹ� ������ �������� �̱� ������ FIQ ��忡�� R8 ~ R12 �� ��������� ������ ���� �ʾƵ� �Ǵ°� �Դϴ�. ������ FIQ ��忡���� R0 ~ R7 �� ����Ѵٸ� ���� ����� ������ �ؾ� ������.

���ذ� ���ó���. ARM ���� 3���� ��쿡 ���ؼ� ���� �ڵ带 �Է��ؼ� ��Ʈ �غ����� �ϼ���. ���������� �ڵ带 �ۼ� �Ҷ� ���� �߿��� ���� �Դϴ�.

6.3.2 Special Registers

ARM �������͵��߿��� R0 ~ R12 ������ �Ϲ� ����, �ӽ� ���� ��ҵ����� ����� �ǰ� R13 ~ R15������ ���� Ư���� �ǹ̸� ������ �ֽ��ϴ�.

���� CPSR(Current Program Status Register) �̶�� ���� �������͵� �ֽ��ϴ�.

(1) R13

- Stack Pointer(SP)

- ARM ���� ��庰�� ���� ������ ����Ű�� �ֽ��ϴ�.

- R13(SP)�� ARM ���� ��庰�� ��ũ�� �Ǿ� �ִ� �������� �Դϴ�.

(2) R14

- Link Register(LR)

- �Լ� ȣ��� ���ϵ� �ּҸ� ������ ����

- R14(LR)�� ARM ���� ��庰�� ��ũ�� �Ǿ� �ִ� �������� �Դϴ�.

�Լ� ȣ��� ������ �ּҸ� �����ϱ� ���ؼ� �������� ���� 1���� �Ҵ��ߴµ� � ������ ������� ?

������ �б�(BL)�ϴ� ��찡 �ƴ� �ѹ��� �б�(BL) �ϴ� �����, �Լ� ���� ������ �ּҷ� �����Ҷ� ������ ������� �ʰ� R14 �������� ��������ν�, �� �ӵ����� ������ ��� �Ǵ� ���Դϴ�.

* ���� ���� = ���� �� ���� = ����

�������ʹ� CPU�� ���� �� �� �ִ� ���� ���� ������ �� ���� ���� �̶�� �����ϸ� �ǰڽ��ϴ�.

(3) R15

- Program Counter(PC)

- PC�� ����Ͽ� ���� ���ɾ Fetch

- R15(PC)�� ���μ��� ��忡 ������� �ϳ��� R15�� ������ ����( ARM ���۸�庰�� ��ũ�� �Ǿ� ���� �ʽ��ϴ�.)

(4) CPSR

- Program Status Register (CPSR)

- CPSR�� ARM ���� ��庰�� ��ũ�� �Ǿ� �ִ� �������� �Դϴ�.

-

���μ��� ��尡 ������ �Ǹ� �ϵ���������� ����DZ� ������ CPSR ���纻�� SPSR( Saved Program Status Register - CPSR�� ��ũ�� ��������) �� ������ �˴ϴ�.

- User, System ��带 �����ϰ� �� ���� ��帶�� �ϳ��� ���� �մϴ�.

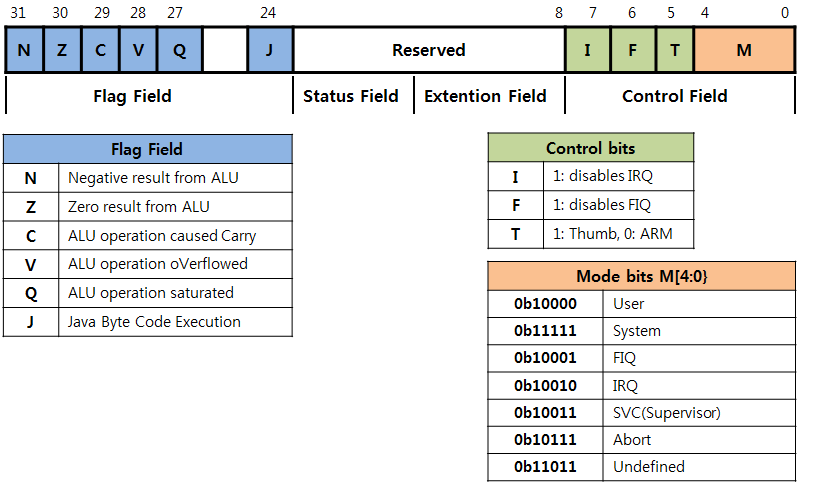

�Ʒ� ���� �� ������ ���̱�� ������ CPSR�� 32bit ���������� ���Դϴ�. ���ݺ��� �ϳ��� ������ ������ ������.

�տ� NZCVQ�� Flag field��� �ؼ�, ���� ������ �Ŀ� set�Ǵ� register�Դϴ�. �� field�� ��� ó���� ALU�� ���� ����� ���¸� ��Ÿ���ϴ�.

1) N : Negative - �������� ���̳ʽ��� ��쿡 set �˴ϴ�.

2) Z : Zero - �������� 0�� ��쿡 set �ǿ�.

3) C : Carry - �������� �ڸ� �ø��� ���� ��쿡 set �˴ϴ�.

4) V : oVerflow : ������ ����� overflow ���� ��쿡 set�Ǵµ�, Over flow��°� ��ġ�� ���ϱ� ���� ������ �ϴ� Range���� ��� ���� ū ��찡 �� ��쿡 �ش�˴ϴ�.

�̰��� �ʿ伺�� ARM�� ö���̱ �ѵ�, ARM core�� Opcode�� Memory���� �������� ���� (Fetch) �̸� ������ �����ϴ� ���� �ƴ϶� Condition flag�� NZCV�� ���� �ٷ� �� opcode�� �������� ���� �������� ������ ������ �� �ֽ��ϴ�.

Default�� AL "Always" , condition�� ������� �� ���� �ϴ� ���Դϴ�. Control Field�� ���ؼ��� �켱 ������� ������ �ϰ�, ARM Instruction���� ���� �ڼ��� ���� �� ������ �ϵ��� �ϰڽ��ϴ�.

Control Field�� 7�� ��Ʈ�� "I" �� 1�� ����ŷ�� �ϸ� ���ͷ�Ʈ�� �� ���� �ʽ��ϴ�. ���ͷ�Ʈ�� �� ���̱� ���ؼ��� 0���� Clear �ؾ� �մϴ�.

���������� Control Field�� 6�� ��Ʈ�� "F" �� 1�� ����ŷ�� �ϸ� Fast ���ͷ�Ʈ�� ���� ���� �ʽ��ϴ�. Fast ���ͷ�Ʈ�� �� ���̱� ���ؼ��� 0���� Clear �ؾ� �մϴ�. ���������� 5�� ��Ʈ�� "T" ��尡 �ֽ��ϴ�. ARM Core�� �ʱ� ���ýÿ��� ������ ARM ���(5�� ��Ʈ�� "T" �� 0���� ���� ��)���� ������ �ǰ� ��쿡 ���� Thumb mode�� ��ȯ�� �� ���� �ֽ��ϴ�. Thumb mode�� ���ؼ��� ������ �忡�� �ٽ� ������ �ϵ��� �ϰڽ��ϴ�. �������� ARM���� 7������ ���� ��尡 �ִٰ� �Ͽ��µ�, �� ���� ���鿡 ���� ���� ǥ�� �� CPSR�� ���� 5bit(Mode bits)�� ������ ������ �˴ϴ�.

6.4 ARM Exceptions

Exception �̶� ������ ���? �������� �ǹ̷δ� "����" ��� �Ǿ� �ֽ��ϴ�. ������ �츮�� ���� ARM�� �����ϰ� �ֱ� ������ ���� ARM ���� ǥ���� �Ѵٸ�,

�ܺ� ��û�̳� ���α� ������ ���� �ڵ��� �������� �帧�� ����� ���� �̶�� ������ �ϰڽ��ϴ�. �ڵ���

�������� �帧�� ����ٴ� �̰���� PC(R15)�� �ּҰ� �ٲ�� �Ǵ� ���Դϴ�. �Ʒ� ���� Exception �߿��� IRQ ���� ��Ȳ�� ������ ��쿡 Exception ó�� �帧�� �⺻���� ���� �Դϴ�.

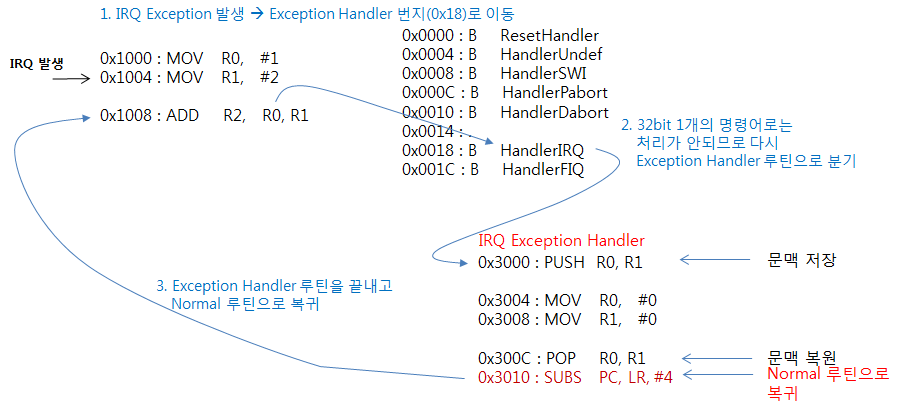

PC�� 0x1004�� �����ϰ� ���� IRQ ���� ��Ȳ�� ������ �ϰ� �Ǹ� �ڵ��� �������� �帧�� ��� �ߴ��ϰ� IRQ ���ܻ����� ó���� �־�� �մϴ�.

���⼭ IRQ���� ��Ȳ�� ó���� �ִ� ��ƾ�� Exception Handler�ϰ� �մϴ�. Exception Handler ������ 7���� ���� ��Ȳ(���� �������� IRQ ����)�� �´� ������ ó���� �ϰ� Exception�� ���ϱ� �������� �����ϸ� �˴ϴ�. Exception Handler���� �Ѱ��� ���� �� ������ Exception�� ���ϱ� �������� �����ϱ� ���� �ݵ�� ������ �����ϰ� ���� �ؾ� �մϴ�.

����

���� �������� ���ǻ� IRQ ���� ó���� ���ؼ� 0x3000������ �ڵ��� �帧�� ����Ǿ����� ������ ARM������ IRQ �� ���ϸ� �ڵ��� �帧��(PC) 0x00000018 �� H/W ������ ������ �ǰ� 0x00000018 ������ �ٽ� ������ ���� ������ ó���ϴ� Exception Handler �Լ��� �б��ϴ� ������� ó���� �˴ϴ�.

0x00000018 ������ Exception Vector��� �ϰ�

ARM������ 7������ Excepton�� �����ϴµ� �̷��� ���� ��Ȳ�� ������ �ϸ� �� ���� ��Ȳ�� ���� �̸� �Ҵ�� �ּҿ� �ִ� ARM ���ɾ ������ �˴ϴ�.

�Ʒ� ǥ�� ARM������ 7������ Excepton �� ���Ͽ� �ּҿ� �� Exception�� �Ҵ�� ������ Vector �ּ� �Դϴ�.

| Exception Type | Priority | Mode | Vector | High Vector |

| Reset | 1 | Supervisor | 0x00000000 | 0xFFFF0000 |

| Undefined Instruction | 6 | Undefined | 0x00000004 | 0xFFFF0004 |

| SWI | 6 | Supervisor | 0x00000008 | 0xFFFF0008 |

| Prefetch Abort | 5 | Abort | 0x0000000C | 0xFFFF000C |

| Data Abort | 2 | Abort | 0x00000010 | 0xFFFF0010 |

| Reserved | 0x00000014 | 0xFFFF0014 | ||

| IRQ | 4 | IRQ | 0x00000018 | 0xFFFF0018 |

| FIQ | 3 | FIQ | 0x0000001C | 0xFFFF001C |

Exception�� ������ �տ��� ����� ARM ���� ������ ���踦 ȥ���ؼ��� �ȵ˴ϴ�. ���� ��Ȳ�� ���ϸ� �� ���� H/W ������ ARM ���� ��尡 ������ �Ǵ� ���Դϴ�. Priority�� ���� �ð��� �ټ��� ���� ��Ȳ�� �����ϰ� �Ǹ� �켱������ ���� ���� ���� ���� �ϰ�����.

���� Vector�ּҴ� 0x00 �������� 32bit(4Byte)������ ���� �ϴµ�, High Vecotr�� ������ �Ǹ� ���� �ּҰ� 0xFFFF0000�� �˴ϴ�. Windows CE������ High Vector�� ����Ѵٰ� �մϴ�.

(1) Reset

ARM Core�� ������ �ΰ��ϴ� ��� ��

| Reset ���� CPSR, Register ���� | |

| R14_svc | UNP |

| SPSR_svc | UNP |

| CPSR[4:0] - ARM ���� ��� | Supervisor Mode |

| CPSR[7:5] - ���ͷ�Ʈ ���� | I=1, F=1, T=0 |

| PC - Vector Address | 0x00000000 |

(2) Undefined Instruction

ARM Processor ���� ���ǵ��� ���� ���ɾ� ���� ���� �ϴ� ��쿡 ��

| Undefined Instruction ���� CPSR, Register ���� | |

| R14_und | Address of the undefined instruction + 4 |

| SPSR_und | CPSR |

| CPSR[4:0] - ARM ���� ��� | Undefined Mode |

| CPSR[7:5] - ���ͷ�Ʈ ���� | I=1, F=unchanged, T=0 |

| PC - Vector Address | 0x00000004 |

| Return | MOVS PC, LR |

Return �̶�� �Ǿ� �ִ� ���� Exception Handler ������ ��ġ�� ������ ���α� �帧���� �����Ҷ�, R14�� H/W������ ���� ���� �ּҿ� ���� ������ �˴ϴ�. �� Exception ������ ���� R14�� ���� ���� �ּҰ� �� ���Ƿ� ���� �ؾ� �մϴ�.

(3) Software Interrupt

�� Ư�Ǹ�忡�� Ư�� ���� �����ϱ� ���ؼ� Software Interrupt ���ɾ ������ ��� ��

| Software Interrupt ���� CPSR, Register ���� | |

| R14_svc | Address of the SWI instruction + 4 |

| SPSR_svc | CPSR |

| CPSR[4:0] - ARM ���� ��� | Supervisor Mode |

| CPSR[7:5] - ���ͷ�Ʈ ���� | I=1, F=unchanged, T=0 |

| PC - Vector Address | 0x00000008 |

| Return | MOVS PC, LR |

(4) Prefetch Abort

Illegal �ּҿ��� ���ɾ �����ͼ� ���� �Ϸ��� ��쿡 ��

| Prefetch Abort ���� CPSR, Register ���� | |

| R14_abt | Address of the aborted instruction + 4 |

| SPSR_abt | CPSR |

| CPSR[4:0] - ARM ���� ��� | Abort Mode |

| CPSR[7:5] - ���ͷ�Ʈ ���� | I=1, F=unchanged, T=0 |

| PC - Vector Address | 0x0000000C |

| Return | SUBS PC, LR, #4 |

(5) Data Abort

Illegal �ּҿ� Data�� ���ų� �б� ������ �õ��ϴ� ��쿡 ��

| Data Abort ���� CPSR, Register ���� | |

| R14_abt | Address of the aborted instruction + 8 |

| SPSR_abt | CPSR |

| CPSR[4:0] - ARM ���� ��� | Abort Mode |

| CPSR[7:5] - ���ͷ�Ʈ ���� | I=1, F=unchanged, T=0 |

| PC - Vector Address | 0x00000010 |

| Return | SUBS PC, LR, #8 (re-executed) SUBS PC, LR, #4 (not re-executed) |

(6) IRQ

ARM Processor �ܺο��� ���ͷ�Ʈ�� ��û�� ��쿡 ��

| IRQ ���� CPSR, Register ���� | |

| R14_irq | Address of the next instruction to be executed + 4 |

| SPSR_irq | CPSR |

| CPSR[4:0] - ARM ���� ��� | IRQ Mode |

| CPSR[7:5] - ���ͷ�Ʈ ���� | I=1, F=unchanged, T=0 |

| PC - Vector Address | 0x00000018 |

| Return | SUBS PC, LR, #4 |

(7) FIQ

ARM Processor �ο��� Fast ���ͷ�Ʈ�� ��û�� ��쿡 ��

| FIQ ���� CPSR, Register ���� | |

| R14_fiq | Address of the next instruction to be executed + 4 |

| SPSR_fiq | CPSR |

| CPSR[4:0] - ARM ���� ��� | FIQ Mode |

| CPSR[7:5] - ���ͷ�Ʈ ���� | I=1, F=1, T=0 |

| PC - Vector Address | 0x0000001C |

| Return | SUBS PC, LR, #4 |

Exception Handler�� �����ϰ� ������ ���μ��� �帧���� �����ϴ� Return ���ɾ��� �������� SUBS, MOVS ������ ���� "S" ���̻簡 ���� �ٽ��ϴ�.

"S" ���̻��� �ǹ̴� Destination �������Ͱ� ���� PC(R15) ��� SPSR�� CPSR�� ���� �϶�� �ǹ��� ���̻� �Դϴ�. ���� �̷��� ������ H/W ������ �̷�� ���ϴ�.

�Ʒ� ���� IRQ ���� ó���ϴ� ���� �Դϴ�. ������ ����ߴ� ������ ���� ���ñ� �ٶ��ϴ�.

���α��� �������� �帧���� 0x1004���� ���ɾ� ó���߿� IRQ ���ܰ� ���ϸ� 0x1004 ������ ���ɾ� ������ �Ϸᰡ �� ���Ŀ� IRQ ������ Exception Vector�� 0x0018������ PC�� �̵��� �ϰ� 0x0018�������� ������ IRQ ����ó�� �ڵ鷯 �Լ��� �ִ� ������ �ٽ� �̵��� �Ѵ���

����ó���� �Ϸ��ϰ� �ٽ�

IRQ ���ܰ� ���� ���� ������ ���ɾ �ִ� ������ "SUBS PC, LR, #4" �� ���ؼ� �����ؼ� IRQ ���ܰ� ������ ������ó�� ����ؼ� Normal ��ƾ�� ������ �˴ϴ�.

������ �Ѱ��� ������ ���߸� ���� �ִµ�, IRQ ���ܰ� �Ͼ�� H/W �����δ� ������ ���� ���� ���� �մϴ�.

(1) CPSR ��� : SPSR_irq = CPSR_svc

(2) ARM ���� ��ȯ( ���ܻ�Ȳ������ �� ARM ���� ������ ��) : CPSR.T = 0

(3)

CPSR MODE �� IRQ ���� ���� : CPSR[4:0] = 0b10010

(4) IRQ ��� ����ŷ(���ͷ�Ʈ�� Disable ��) : CPSR.I = 1

(5) R14_irq = PC + #8

(6) PC = 0x18( IRQ Vector address)

(5)�� �� LR(R14)�� PC + #8�� ���� ������ Ư�� ������ ���ɾ ����ɶ� IRQ�� ���� �ϸ�

Execution - Fetch - Decode �� Pipe line ���� ���� Execution �ܰ迡�� ���� PC�� ���� �������� ���ɾ��� Fetch(+4), Decode(+8) �ܰ谡 ������ �ǰ� �ֱ���� LR���� PC + #8 ������ ���� ��� ���� �˴ϴ�. ������ IAR, KEIL, ADS ���� �����Ϸ� ����� IRQ���� LR�������� ���� �����غ��� LR�� ���� PC + #8 �� �ƴϰ� LR = PC �� ���� �����ϴٰ� ǥ�� �˴ϴ�. �̰��� �����Ϸ� ������� ȥ���� ���ϱ� ���ؼ� �̷��� ǥ�ø� �ϰ� �ִ°� �����ϴ�.

6.5 Exception �� Interrupt�� ����

Exception��

Interrupt�� ������ �ٸ����. ��쿡 ���� ����� �ǹ� �ϼ��� �ֽ��ϴ�. ������ ��� �ٸ����� �ֽ��ϴ�.

(1) Exception

- Ư�� ���ɾ� ��� ���� ������ ��

- Ŭ�Ͽ� ���� ������ ���� : Exception�� �ַ� Core���ο��� ���ϱ� ������ Core�� Ŭ���� ���������� ���� �մϴ�.

- �� ���� ����, ����� �ߴ���, divide by zero... ��

- �а� �����ϸ� Exception�� IRQ�� �����Ѵٰ� �����ص� �˴ϴ�.

(2)

Interrupt

- Processor �� ���ɾ� ����� ������� Processor �ܺο��� �ַ� �� --> Ŭ�Ͽ� �� ������ �� �Ҽ��� ����

6.6 ARM������ Interrupt system

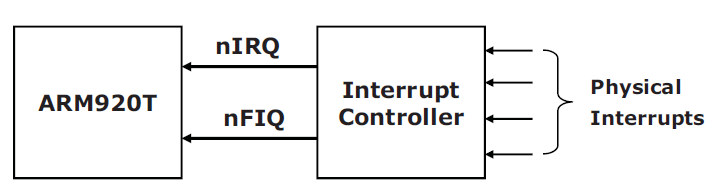

ARM Cortex�ø��� ������ �������� ARM Core���� ���ͷ�Ʈ�� �� �帱 �� �ִ� �����

IRQ, FIQ 2���� �ۿ� �����ϴ�.

���� ���� ARM9 Core�� ���ͷ�Ʈ ������ �Դϴ�. Interrupt Controller �� Physical Interrupts(UART, I2C ��) �ҽ��� ARM Core ������ ������ �ƴմϴ�. Interrupt Controller �� Physical Interrupts �κ��� ARM Core�� �̿��ؼ� ������ S3C2440���� CPU ���� �Դϴ�. �ٽ��ѹ� �����帮���� ARM Core���� IRQ�� FIQ�ĸ��� �� ���� �� �ֽ��ϴ�. Interrupt Controller�� CPU Vendor�� ���ؼ� �ٸ��� ������ �ɼ��� �ֽ��ϴ�.